国创中心张祥:车规芯片功能安全要求和设计概览

6月29日-30日,由盖世汽车主办的“2021中国汽车半导体产业大会” 隆重召开。本次会议主要围绕中国车企缺芯现状、供应链国产化安全建设、车载芯片平台的搭建设计、自动驾驶、智能座舱领域的芯片需求和应用案例、功率半导体在三电中的应用以及芯片测试和功能安全等话题展开讨论,共谋产业未来发展之路。下面是国家新能源汽车技术创新中心功能安全总师张祥在本次大会上的演讲。

国家新能源汽车技术创新中心功能安全总师张祥

各位朋友上午好,我是来自国创中心的张祥。国创中心是在科技部推动下成立的第二家国家级技术创新中心,主要专注在新能源汽车领域,包括整车、零部件及车规半导体。我本人主要从事车规芯片功能安全相关的工作,下面我也将从车规芯片功能安全角度跟大家分享一下我们的理解。

随着汽车电子智能化程度不断提升,车规芯片的使用量也在不断增加。为了保障交通参与者,包括驾驶员、行人、乘客的安全,业内对于汽车安全性的要求也在不断提升。通常我们要求车规芯片满足“零缺陷”要求,这也是我们在车规芯片领域一直追求的目标。在高可靠性的基础上,随着技术复杂度的提升,我们对车规芯片功能安全的要求也在提高,从而消除和控制系统性失效和随机硬件失效带来的风险。车规芯片的非功能性要求包括:可靠性,维修性,测试性,保障性,环境适宜性和安全性,其中安全性是我们关注的重点。

这里简单列举了一下目前国内外有关功能安全标准的情况。最早发布的功能安全标准是IEC 61508标准,在这个标准基础上衍生出了像ISO 26262,EN 50129等针对不同领域的功能安全标准。尽管这些标准中也包含了一些实现层面的指导,但它们更多侧重于总体要求,并且未对不同应用进行细分。这里也列举了一些功能安全国家标准,与国际标准相对应,我们也制定了功能安全的总体标准GB/T 34590。表格中后几项国内标准与国际标准有所不同,这几项标准会针对不同的应用(包括电池管理系统,电机控制系统,转向系统等),提出相应的功能安全标准,从而将标准落地,推动功能安全在国内的实施。另外需要注意的是,在ISO 26262:2018和国标第二版中,新增了半导体功能安全相关的章节。新增内容详细描述了功能安全在半导体领域的基本概念和理论,并列举了不同类型的半导体器件中需要考虑功能安全方面的要求,这不仅可以作为半导体从业者开发芯片时的指导,也为OEM和Tier1更好的选择与评估芯片提供了参考。

根据功能安全标准中的要求,功能安全是遵循“V模型”进行开发和验证的,其中“V模型”左侧侧重于设计,“V模型”右侧则侧重于验证和测试。无论是针对芯片或者系统,功能安全均需要对系统性失效和随机硬件失效进行处理。对于系统性失效通常通过遵循一定的开发流程来避免和控制,没有定量的指标去衡量。对于随机硬件失效则通过安全架构设计对其进行探测和控制,需要同时满足单点故障度量、潜伏故障度量和随机硬件失效目标估值的要求。此外,车规芯片功能安全应考虑其全生命周期过程,且在不同阶段功能安全均应得到满足和达成。

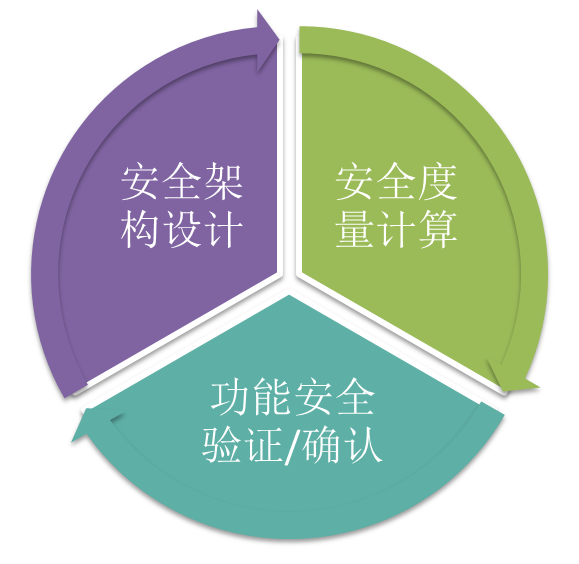

车规芯片功能安全设计需遵循功能安全相关标准(如ISO 262626以及GB/T 34590)中的要求,但由于芯片的特殊性,我们在进行车规芯片功能安全开发时会对标准中规定的流程进行裁减,留下适合于芯片的部分。在开发过程中,有三个层面需要重点关注:安全架构设计、安全度量计算以及功能安全验证和确认。安全架构设计是功能安全开发的核心,我们需要通过设计合理的安全架构,实现对系统性失效和随机硬件失效的控制。安全度量计算通过定量计算来检验功能安全设计对于随机硬件失效的探测和控制能力,而功能安全验证和确认活动对功能安全开发活动的正确性和完整性进行检验。

首先我们看一下安全架构设计部分,简单来说可以分为三个步骤:获取车规芯片顶层安全要求;通过安全分析推导违反顶层安全要求的失效模式;针对失效模式进行功能安全设计,包括设计安全机制和安全措施等。对于顶层安全要求的推导,通常来说会有两种方法:第一种方法是基于特定应用要求逐级推导获取芯片顶层安全要求,通常适用于应用在特定应用下的芯片开发。第二种方法是基于SEooC(独立于环境的安全要素)方式获取芯片顶层安全要求,这种方式可以使芯片适用于多种应用,也是目前较为普遍采用的方法。在得到了安全要求之后,可以通过例如FMEA以及FTA等安全分析方法,推导获取违反安全要求的失效模式。针对违反安全要求的失效模式,需要设计安全机制以及安全措施,以保证功能安全要求得到满足。安全机制的选择是比较重要的内容,需要考虑如ASIL等级要求,故障处理时间间隔以及实现难度和成本等因素。

在功能安全标准中列举了一系列的安全机制的示例,我们可以作为参考来使用,并在此基础上进行扩展。当然安全机制在选择时需要考虑其有效性,需要对随机硬件失效和系统性失效有很好的控制作用。对于芯片层级,安全机制通常包括两种类型:内部安全机制和外部安全机制。内部安全机制由芯片提供方负责实现,并需要对其有效性提供证明。外部安全机制是由芯片集成/使用方负责实现并保证其有效性。如果我们仔细查阅芯片安全手册会发现,其实两种方式是并存的,只使用内部安全机制会造成芯片成本的增加,只使用外部安全机制则会增加芯片使用者的负担和工作量,因此目前已应用的芯片通常是在内部安全机制和外部安全机制之间选取平衡点。这里还有一个重要指标,就是安全机制的诊断覆盖率(DC,Diagnostic Coverage)值。诊断覆盖率简单来说就是安全机制对失效的探测程度,比如诊断低覆盖率值的典型值之一99%就是说有99%的失效可以被此安全机制探测到。诊断覆盖率值的声明依据可以来自于标准,可来自理论计算和仿真,也可以来自于专家判断,还有一些是通过测试的方式获得的。当然诊断覆盖率值也会受到一些影响,比如说相关失效影响会降诊断低覆盖率,这在芯片设计过程中也是需要加以考虑。

这里有一个关于CPU的功能安全设计示例。如果要满足ASILD等级要求,我们要对系统性失效和随机硬件失效有比较好的控制。那么落实到CPU部分怎么做呢?比较通用的架构是双核锁步(Lockstep)结构。

在此结构下,虽然我们使用了两个CPU内核,但是性能依旧是单核的性能,带来的益处是通过周期性比较两个CPU的输出结果,保证了CPU运算结果的正确性。这个机制看起来很简单,但在实际操作中需要考虑很多因素。例如为了防止相关失效的影响,需要进行“异构”的设计,包括双核内部结构的异构、执行时序的异构、物理位置的异构等。此外还需要设置物理隔离防护等措施,从而保证两个CPU内核进行独立的运算处理。这个示例是我们在设计CPU功能安全时的一个典型方式。这种设计方式不仅在微控制类芯片中较常采用,在高性能芯片设计中也会采用类似的方式进行处理。

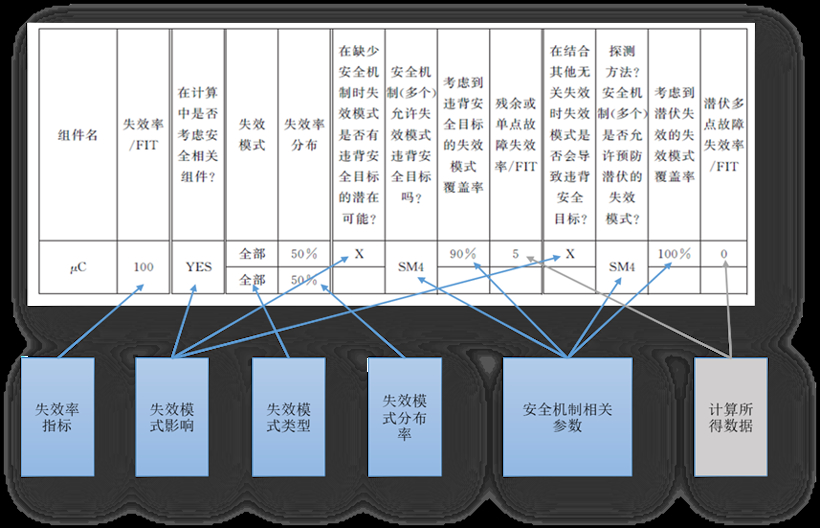

接下来我们看一下安全度量计算,这部分主要针对随机硬件失效。针对不同的ASIL等级要求,其中一个要求是将随机硬件失效控制在一定范围内,并且同时满足单点故障度量,潜伏故障度量和随机硬件失效目标值的要求。关于定量指标,在标准里面有非常明晰的公式,也有一些例子,所以实施起来难度并不大。但是计算过程中需要确定一系列参数值,这些参数的确定才是功能安全定量计算中的难点。

如上图所示,这些方框中的参数包含了基础失效率、失效模式定义、失效模式分布、安全机制覆盖率声明数值等,所有这些数据的获取都需要理论和证据支撑,有些甚至需要通过大量测试得到。

举例来说,针对基础失效率,通常需要包含永久性基础失效率和瞬态失效率两种。对于这两种类型的失效,都需要在定量计算里面加以考虑。对于永久性基础失效率,通常有三种方式获取:第一种方式是使用或基于行业来源计算永久性基础失效率,第二种方式是使用现场数据统计计算永久性基础失效率,第三种方式是从试验测试中推导获得的失效率。通常来说,第一种方式获取的数据会比较保守,但好处是简单易实施,可以直接通过读取标准获取信息,这也是业内使用比较多的一种方式。第二种方式难度在于要收集足够的现场数据样本,如果样本不够充分,则数据统计结果就会不准确。第三种需要进行特定的试验,因此会增加成本和试验周期。对于瞬态失效,一般我们会重点考虑α粒子和中子的影响,可遵照JESD89A标准定义的测试方法,对瞬态故障失效率进行测量。

车规芯片功能安全考虑中的第三部分是验证和确认。无论是对于汽车电子零部件还是半导体,功能安全验证和确认都是必不可少的过程,它主要对应于“V模型”的右侧。从功能安全标准里可以看到,Part 5对于硬件部分的要求也适用于半导体层级,除了走查、检查和安全分析的方式外,仿真和原型验证也是芯片开发过程中重要的手段。为了验证半导体级硬件安全要求实施的完整性和正确性,硬件集成测试需要遵照ISO 262626:2018-5和ISO 262626:2018-11中的要求。这里我反复提及了功能安全标准,但标准其实是我们进行功能安全设计的一个起点,也并不是说只要满足标准要求就可以了。标准中的要求是最低的要求,随着我们技术的不断积累会衍生出比标准更高更全面的要求,从而指导我们进行设计。

再谈一下故障注入,这个技术是在功能安全领域应用较多,在半导体领域尤为重要。故障注入可用于支持生命周期的若干活动,包括硬件度量评估,安全机制的诊断覆盖率评估,故障探测时间间隔和故障影响时间间隔的评估,故障影响的确认等。通常我们在EDA仿真环境下使用这种技术多一些,因为随着芯片实体开放接口和封装后形式的限制,我们所做的故障注入会受到一些限制。通常EDA环境下也会集成一系列工具,可以帮助我们方便的实施这样的操作。

简单总结一下,随着汽车电子系统功能安全要求的不断提升,在满足可靠性的同时,对车规芯片安全性的需求也在不断加强,其中符合功能安全要求已经成为了很多车规芯片“必需”的属性。汽车电子复杂度的提升也带来了对于芯片的更高要求,如何设计生产出国产高安全性车规芯片是亟待解决的“掐脖子”问题,这就需要对技术难关进行攻克,并不断总结和积累经验。

未来随着自动驾驶技术的发展,高算力芯片以及可编程器件在车端的应用不断加强,保证此类芯片和器件的功能安全设计满足要求,是必然的趋势。功能安全设计虽然提升了安全性,但是由此也带来了芯片研发成本以及价格的提升,最终我们在设计芯片的时候会折中做一个选择,设计出一个真正符合市场要求的芯片。此外预期功能安全作为对功能安全的补充,提升了车辆的整体安全性。如何将预期功能安全与功能安全融合,并在芯片层级助力其实现,也是未来需要思考和解决的问题。

我演讲的内容就是这些,可能更偏向于技术层面一些,希望能给大家带来一些收获,谢谢大家的时间!